# Programming with Explicit Dependencies

A Framework for Portable Parallel Programming

# **Programming with Explicit Dependencies**

A Framework for Portable Parallel Programming

Eva Burrows

Dissertation for the degree of philosophiae doctor (PhD) at the University of Bergen

March 2011

ISBN 978-82-308-1730-8

© Eva Burrows, 2011

Parts of this publication are copyrighted by Elsevier Inc.  $\ @$  2009 hereby reused under the authors' Retained Rights policy.

Published by the University of Bergen, Norway, 2011 Printed by AIT

#### **MOTTO**

Remember your Creator in the days of your youth,

Before the difficult days come, and the years

draw near when you say, "I have no pleasure in them" (...)

For man goes to his eternal home,

And the mourners go about the streets.

Remember your Creator before the silver cord is loosed,

Or the golden bowl is broken,

Or the pitcher shattered at the fountain,

Or the wheel broken at the well.

Then the dust will return to the earth as it was,

And the spirit will return to God who gave it.

"Vanity of vanities," says the Preacher,

"All is vanity." (...)

And further, my son, be admonished by these. Of making many books *there is* no end, and much study *is* wearisome to the flesh.

Let us hear the conclusion of the whole matter:

Fear God and keep His commandments,

For this is man's *all*.

For God will bring every work into judgment,

Including every secret thing,

Whether good or evil.

Ecclesiastes 12

# Preface

When I set off on my Norwegian saga to obtain a PhD in computer science, I soon realised how little prepared I was for the challenges that would have to face on the long run, truly I was unprepared and naive. Making the decision to embark on a journey like this took several years, and it brought about a series of life-changing events, e.g., moving country, leaving behind family and friends, and quitting Koinónia – a Romanian publisher where I had spent most of my time working as IT Manager for more than a decade by then.

My return to academia began with a two years study leave from my employment to obtain a Master's Degree in Programming Theory from the Department of Informatics at the University of Bergen. Marc Bezem, who supervised me at the time, tried to entice me to enrol on a PhD training right away. I was, however, rather uncertain about this, and upon my graduation I duly returned home.

During the years of my master studies, I had the opportunity to get an insight into Magne Haveraaen's research agenda on algebraic software methodologies. In the first year, he was my professor for a course on algebraic program specification, and in the following year, he asked me to be his teaching assistant for the course.

When I made up my mind about my PhD, I contacted Magne inquiring about the prospect of working with him. His most positive reply, finally, removed all my remaining doubts.

The journey since then has been long, enriching but tiring, uplifting and depressing. Sometimes all in the same time. I have learnt many a thing about computer science, research, academia and life. This knowledge, I hope, will stay with me on the journey onward.

#### ACKNOWLEDGEMENTS

I remain indebted to Magne for his unceasing advice and support which provided me with the knowledge, determination and confidence to complete this dissertation. The long, enlightening discussions from the wonders of algebraic abstractions to the beauty of analog photography have always been a source of excitement and refreshment. In the same time, my gratitude goes to Mary Sheeran for taking me onboard, in the first place, and becoming my co-advisor despite her busy schedule, and her constant "How are things?"-check-ups. Her challenging remarks have improved a great deal the breadth and depth of my work. Her workload and attitude in responding my emails within ten minutes, and providing me usually with all the answers I needed, will always remain an example to follow.

The Department of Informatics at the University of Bergen provided me with financial support, a nice office, and countless opportunities for travelling, all of which I am most grateful for. The conferences I have been to were most beneficial for my professional development and networking. I thank my direct colleagues Anya Helene Bagge and Valentin David who helped me in getting through the "PhD system". I hardly ever had a technical or not so technical question that Anya did not have an answer for and has always been a source of information throughout my research. I also thank Ida Holen, Liljan Myhr, Maria Marta Lopez and Tor Bastiansen for doing such a great job in the administration, and getting things done so smoothly.

Many thanks go to people outside the academia, too. Ruth and Magnus Frantzen have become my Norwegian parents, and have shown affection, love and support the way that only parents can do. Their presence made a huge difference to my stay in Norway, for which I am most thankful. Éva Bartha, Ildikó Orbán, Éva Doepp, Ágnes Bálint and Erzsébet Visky have been my best friends for the past 15 years. They are the kind of persons one can always rely on. Their friendship and support have always meant a lot.

I am most grateful to my parents for just simply ALWAYS being there for me. Sadly, my mother passed away before she could have witnessed this happy day with the rest of my family, to whom many thanks go, too: my brother Sanyika, his wife Lucsi and their daughter Anna. Their love and kindness have always welcomed me. I am also grateful to my new family, especially my mother-in-law Dorothy. Her constant love and support have been a great source of encouragement throughout these years.

Love and countless thanks go to my husband, Andrew, for all his tender care, love and kindness, support, friendship and wisdom that helped me through many of the hickups of this journey and of my life.

Finally, but not least, my foremost gratitude, praise and thanks go to God, for His unfailing love that saved me, and for the blessings of intelligence, ambition and strength He granted me to complete this dissertation. Soli Deo Gloria!

# **Contents**

| Pr | eface |                                                 | vii |

|----|-------|-------------------------------------------------|-----|

| Li | st of | Figures                                         | xii |

| 1  | Intr  | oduction                                        | 1   |

|    | 1.1   | Parallelism Going Mainstream                    | 2   |

|    | 1.2   | Program Dependence                              | 3   |

|    | 1.3   | A DDA-based Parallel Programming Model          | 4   |

|    | 1.4   | Contribution                                    | 6   |

|    | 1.5   | Published Results                               | 7   |

|    | 1.6   | Outline                                         | 7   |

| 2  | Con   | quering Parallelism                             | 9   |

|    | 2.1   | T                                               | 11  |

|    |       | 2.1.1 Automatic Parallelization                 | 11  |

|    |       | 2.1.2 Restructuring Compilers                   | 15  |

|    |       | 2.1.3 Data-driven Paradigms                     | 16  |

|    |       | 2.1.4 Parallel Functional Languages in the 90's | 17  |

|    |       | 2.1.5 Explicit Data Dependency                  | 18  |

|    | 2.2   | High-level Approaches in the Multi-Core Era     | 19  |

| 3  | Prel  | iminaries                                       | 25  |

|    | 3.1   | Mathematics                                     | 25  |

|    |       | 3.1.1 Sets                                      | 25  |

|    |       | 3.1.2 Arithmetics                               | 27  |

|    |       | 3.1.3 Relations                                 | 28  |

|    |       | 3.1.4 Functions                                 | 28  |

|    |       | 3.1.5 Graphs                                    | 31  |

|    | 3.2   | Program Code Style Conventions                  | 31  |

|    |       | 3.2.1 Language Constructs                       | 31  |

|    |       | 3.2.2 Guards                                    | 32  |

|   |      | 3.2.3       Data Types                             |

|---|------|----------------------------------------------------|

| 4 | Dat  | a Dependency Algebras 3                            |

| • | 4.1  | A Gentle Introduction to DDAs                      |

|   | •    | 4.1.1 DDAs vs. Classical Graph Representations 4   |

|   |      | 4.1.2 The Expressive Power of DDAs                 |

|   |      | 4.1.3 Structuring DDAs 4.                          |

|   | 4.2  | DDAs for Computations                              |

|   | 4.3  | Space-Time DDAs                                    |

|   | 10   | 4.3.1 DDA-Embeddings                               |

|   |      | 4.3.2 Shared Memory Model 6                        |

|   |      | 4.3.3 Hypercube 6.                                 |

|   |      | 4.3.4 Omega Network 6.                             |

|   |      | 4.3.5 CUDA Programming Model 6                     |

|   | 4.4  | DDA-Projections                                    |

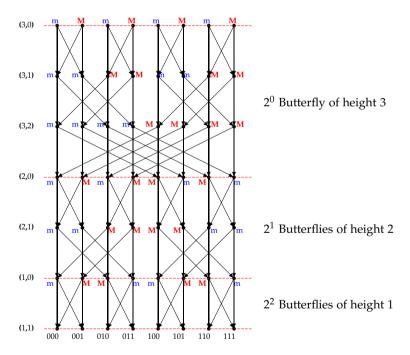

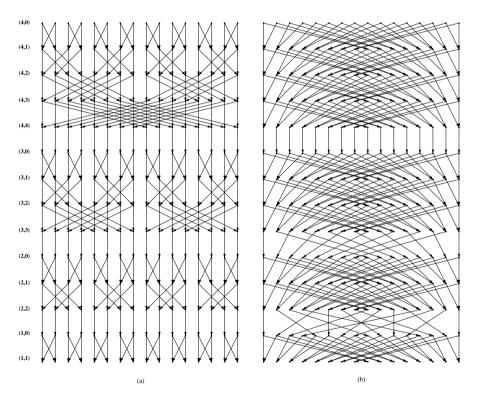

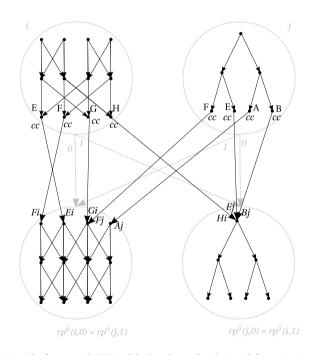

|   |      | 4.4.1 Variations on the Butterly Theme             |

|   |      | 4.4.2 An Example of Non-injective DDA-Embedding 70 |

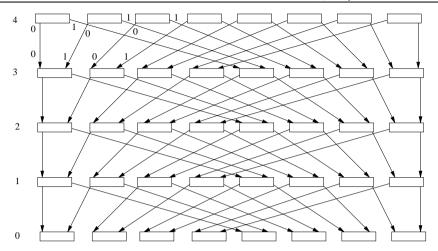

| 5 | DD   | A-based Execution Models 8                         |

|   | 5.1  | The Repeat Statement                               |

|   | 5.2  | Dependency-driven Computation                      |

|   | 5.3  | Space-time Controlled Repetition                   |

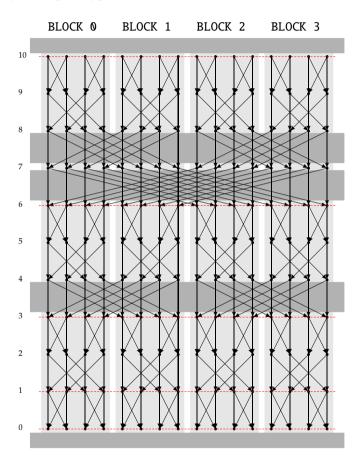

|   |      | 5.3.1 Shared Memory Model Execution                |

|   |      | 5.3.2 Message Passing Execution Model 10           |

|   |      | 5.3.3 The CUDA Execution Model 10.                 |

|   |      | 5.3.4 FPGA Programming                             |

| 6 | Prog | gramming with Data Dependencies                    |

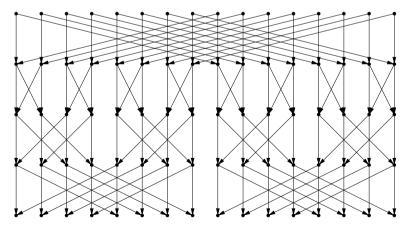

|   | 6.1  | Bitonic Sort DDA                                   |

|   |      | 6.1.1 Shared Memory Model                          |

|   |      | 6.1.2 Hypercube Embedding                          |

|   |      | 6.1.3 CUDA Embedding                               |

|   |      | 6.1.4 Shuffle Network                              |

|   | 6.2  | Odd-Even Merge Sort                                |

|   | 6.3  | Fast Fourier Transform                             |

|   | 6.4  | The Sklansky Parallel Prefix Network               |

|   | 6.5  | Tools                                              |

|   | 6.6  | Experiments                                        |

| 7 |      | ebraic Properties of DDAs                          |

|   | 7.1  | DDA-Combinators                                    |

|    |                           | 7.1.1  | The Parallel DDA-Combinator               | 148 |

|----|---------------------------|--------|-------------------------------------------|-----|

|    |                           | 7.1.2  | The Serial DDA-Combinator                 | 150 |

|    |                           | 7.1.3  | The Sub-DDA-Combinator                    | 158 |

|    |                           | 7.1.4  | The Nesting-DDA-Combinator                | 159 |

|    | 7.2                       | Progra | amming with Compound DDAs                 | 166 |

|    |                           | 7.2.1  | The Transfer Function                     | 166 |

|    |                           | 7.2.2  | Language Constructs for DDA-Combinators   | 166 |

|    |                           | 7.2.3  | An Example of "Combining" the Combinators | 171 |

|    | 7.3                       | Comp   | ile Time Optimizations                    | 174 |

| 8  | Disc<br>8.1<br>8.2<br>8.3 | Conclu | olia: a DDA-enabled Compiler              | 182 |

| St | ımma                      |        |                                           | 185 |

| A  | 24022                     | me     |                                           | 187 |

|    | crony                     | 1113   |                                           | 107 |

# List of Figures

| 1.1  | A Hardware Independent Parallel Programming Model            | 4  |

|------|--------------------------------------------------------------|----|

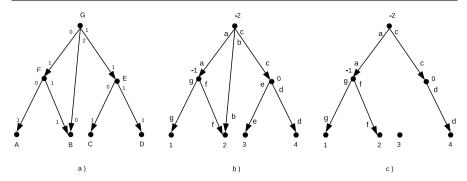

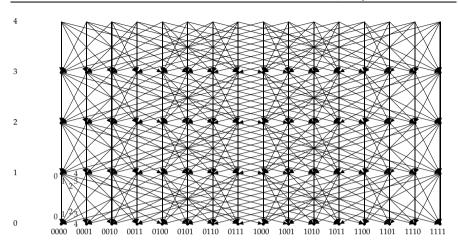

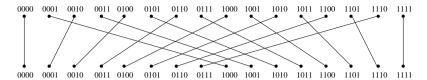

| 4.1  | Simple data dependency graph                                 | 41 |

| 4.2  | Simple data dependency graph modified                        | 44 |

| 4.3  |                                                              | 46 |

| 4.4  | Isomorphic DDAs                                              | 47 |

| 4.5  |                                                              | 47 |

| 4.6  | Non-isomorphic DDAs                                          | 48 |

| 4.7  | Forking DDA                                                  | 51 |

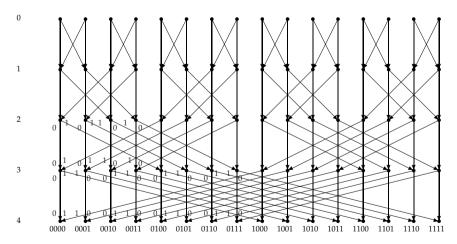

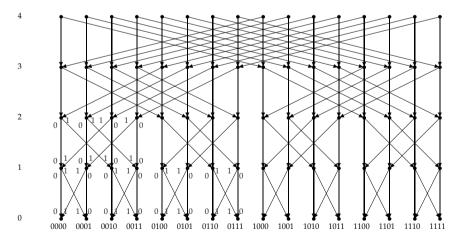

| 4.8  | Butterfly DDA                                                | 52 |

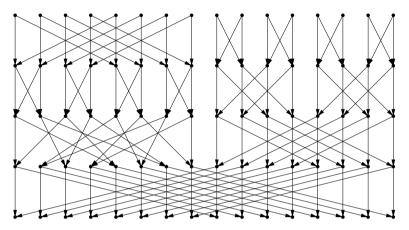

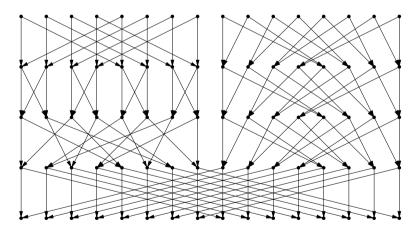

| 4.9  |                                                              | 54 |

| 4.10 |                                                              | 55 |

| 4.11 | Shared memory space-time DDA                                 | 61 |

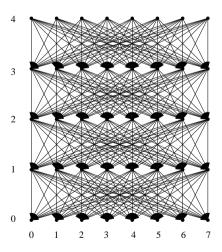

| 4.12 | Hypercube space-time DDA                                     | 63 |

|      |                                                              | 64 |

|      |                                                              | 65 |

|      |                                                              | 70 |

|      |                                                              | 72 |

| 4.17 | Butterfly DDA with alternative layout no. 3                  | 72 |

| 4.18 |                                                              | 73 |

|      |                                                              | 74 |

|      |                                                              | 75 |

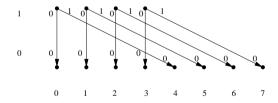

| 4.21 | Shuffled butterfly DDA embedded into smaller omega network . | 77 |

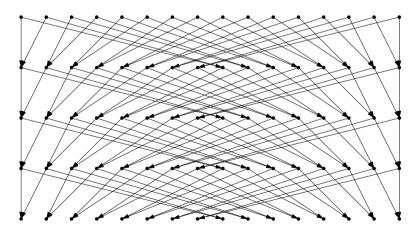

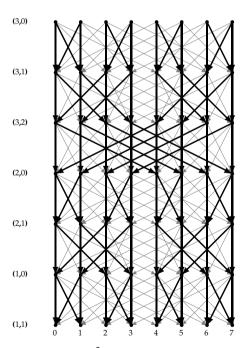

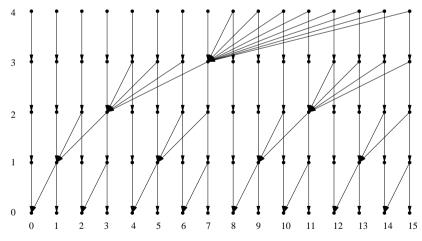

| 6.1  | Bitonic sort DDA                                             | 22 |

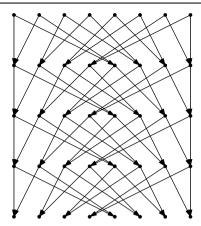

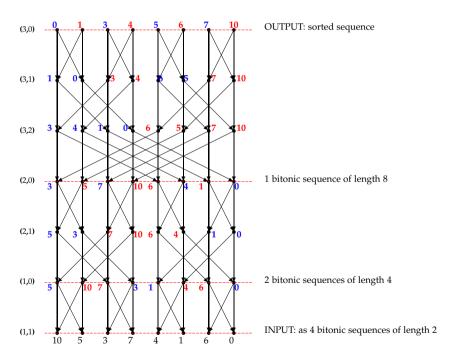

| 6.2  | Bitonic sort DDA in action                                   | 23 |

| 6.3  |                                                              | 26 |

| 6.4  |                                                              | 27 |

| 6.5  |                                                              | 28 |

| 6.6  | Alternative bitonic sort DDA with shuffle projections 1      | 29 |

| 6.7  | Specialised shuffle network for bitonic sorting      | 130 |

|------|------------------------------------------------------|-----|

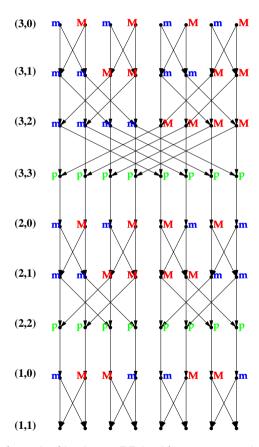

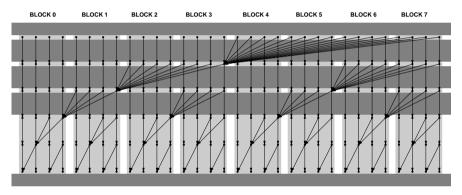

| 6.8  | Odd-even merge sort DDA                              | 133 |

| 6.9  | Odd-even merge sort DDA with CUDA embedding          | 136 |

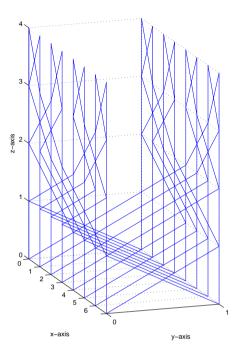

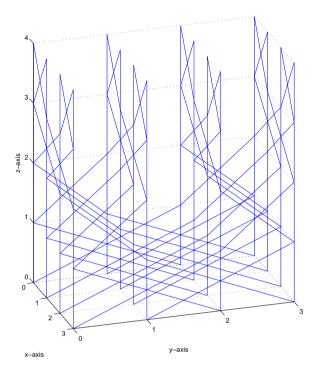

| 6.10 | Radix-2 Fast Fourier Transform DDA                   | 139 |

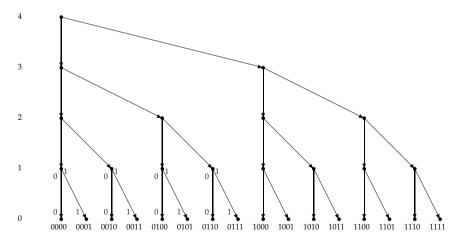

| 6.11 | Sklansky parallel prefix network DDA                 | 141 |

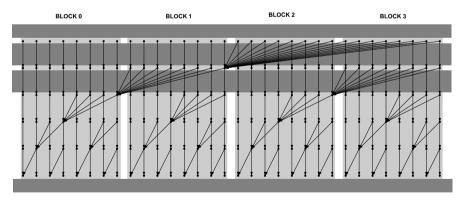

| 6.12 | Sklansky parallel prefix with CUDA embedding for T=4 | 143 |

| 6.13 | Sklansky parallel prefix with CUDA embedding for T=8 | 143 |

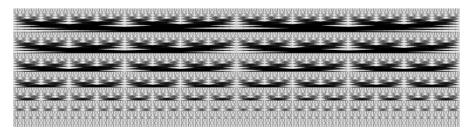

| 6.14 | Generated bitonic sort dependency for 512 inputs     | 145 |

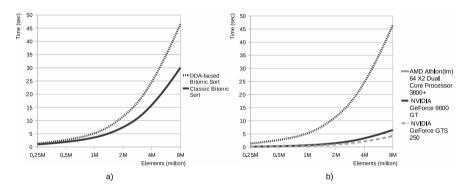

| 6.15 | DDA-based bitonic sort running times                 | 146 |

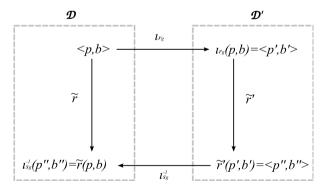

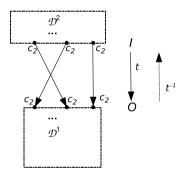

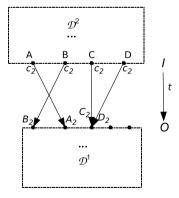

| 7.1  | Serial combination of DDAs along a bijection         | 152 |

| 7.2  | Serial combination of DDAs along a total function    |     |

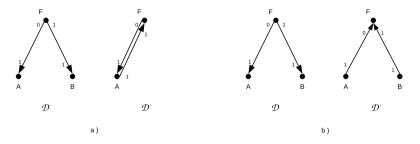

| 7.3  | Nesting DDAs                                         | 160 |

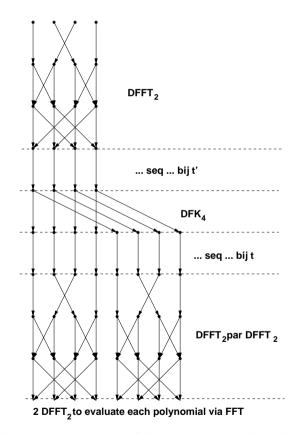

| 7.4  | Polynomial Multiplication DDA                        | 172 |

CHAPTER **I**

# Introduction

The potential of parallel computing became evident more than four decades ago. Powerful parallel systems began to appear, and the initial impression that programming such machines was far from obvious has prevailed. The expanding universe of computing architectures was classified in many different ways, e.g., Flynn's famous taxonomy [Flynn, 1972]. These classifications, however, were derived from the execution models of the systems, and said little about how to program them. As Luc Bougé pointed out [Bougé, 1996], massively parallel machines seemed to have developed so quickly that little time was left to design suitable languages. Therefore, the tendency was to reflect the architecture in an architecture specific programming language, typically by starting with a widely used programming language and extending it with a construct for each hardware feature. This resulted in programming models that were mere subsets of the hardware execution models, and could hardly survive or adapt when new systems appeared. This pointed towards the need of higher level parallel programming models which would abstract from low-level hardware details, so that a programmer need not bother about these [Danelutto et al., 1992; Feldman, 1979; Greif, 1977; Skillicorn, 1995].

Over the last decade, the Message Passing Interface (MPI) [Gropp et al., 2000] and OpenMP [Chandra et al., 2000] have become the two most dominant parallel programming models. They have been taken on board by high-performance computing communities and compiler vendors.

MPI is a distributed memory model, which comes as a standard library and is available on almost every parallel platform. It can be used on networks of workstations as well as on parallel supercomputers. The user writes program code for every participating (parallel) process, and manages the communication between processes by message passing. This is time-consuming and error-prone (e.g. deadlocks, livelocks, etc.). MPI implementations are claimed to be portable, yet they may need adaptations from platform to platform to be more appropriate for the target system.

OpenMP is a shared memory model of parallel hardware, and may achieve better performance than MPI in such an environment. OpenMP is based on a set of compiler directives applied on top of a standard language (e.g. C, Fortran, OCaml). Parallel regions are identified and annotated by the user. In general OpenMP follows a fork-join execution model.

While MPI can easily be adapted to shared memory parallel systems, OpenMP does not scale efficiently to distributed memory parallel systems. However, strategies have been proposed for implementing OpenMP on clusters [Chapman, 2005].

#### 1.1 Parallelism Going Mainstream

Computational devices are now rapidly evolving into massively parallel systems. The number of processors per chip is expected to double every other year or so over the next few years, bringing parallel processing into the mass market. Multi-core processors are standard, and high-performance processors such as the Cell processor [Chen et al., 2007] and graphics processing units (GPUs) featuring hundreds of on-chip processors are all developed to deliver high computing power. They make parallelism commonplace, not only the privilege of expensive high-end platforms. As a consequence, software needs to be parallelized and ported in an efficient way to massively parallel, possibly heterogeneous, architectures. However, current parallel programming paradigms cannot readily exploit these highly parallel systems. In addition, each hardware architecture yet again comes along with a new programming model and/or application programming interface (API). This makes the writing of portable, efficient parallel code even more difficult.

One way of transforming many-core power into real application performance – an approach adopted by most hardware vendors – is to provide libraries, APIs or some ready-to-use software toolbox that help developers to annotate legacy code with parallel constructs where possible (e.g. [Intel, 2009, 2010; Reinders, 2007]). Industry leaders have also joined forces to develop OpenCL, a low-level cross-platform open standard for heterogeneous parallel programming [Khronos, 2010]. OpenCL exposes everything of the underlying platforms and abstracts very little, ultimately hoping to become a target itself for higher level frameworks [HPC Wire, 2010].

The programming community is still in great need of high-level parallel programming models to adapt to the new era of commonly available parallel computing devices as well as to the increasingly more accessible realm of high-performance computing facilities. Parallel computing research blooms like never before. While in the early years of computing parallelism seemed to be desirable for high throughput, by today taking parallelism into account has become inevitable:

"The «not parallel» era we are now exiting will appear to be a very primitive time in the history of computers when people look back in a hundred years. The world works in parallel, and it is time for computer programs to do the same... In less than a decade, a programmer who does not «Think Parallel» first will not be a programmer." [Reinders, 2010]

#### 1.2 Program Dependence

One of the major issues in parallelizing applications is to deal with the underlying inherent dependency structure of the program. Data dependency graphs can abstract how parts of a computation depend on data supplied by other parts. This served as a basis for parallelizing compilers [Banerjee et al., 1993; Wolfe, 1996], and proved that the idea of embedding a program's communication structure into the hardware topology was a reasonable approach. However, automatic dependence analysis is difficult for the general cases, and as a result parallelizing compilers cannot make the most of the underlying dependencies.

The constructive recursive (CR) approach proposed by Haveraaen [2000] allows the modular separation of computation from its dependency, such that both become programmable independently from each other. Dependencies are captured by algebraic abstractions – Data Dependency Algebras (DDA) – and turned into explicit, programmable entities in the program code. DDA-abstractions can also be used to describe hardware communication topologies. Then mapping the computation to a target architecture can be dealt with at a high-level, using DDA-embeddings.

This dissertation presents a framework for portable parallel programming based on DDA-abstractions. Two main issues of parallel computing are addressed: how to map efficiently computations to different parallel hardware architectures, and how to do this at a low development cost, i.e., without rewriting the problem solving code. Today's most widespread parallel programming paradigms and APIs encourage programmers to disregard the underlying hardware architecture in the name of "user friendliness"

– a line supported by most hardware vendors. Our proposed approach, on the other hand, gives direct access to the hardware communication structure but at a high-level. Direct access to aspects of the hardware model is needed by some architectures, e.g., graphics processors. However, the model is fully portable and not tied to any specific processor or hardware architecture, due to the modularisation of the data dependencies.

## 1.3 A DDA-BASED PARALLEL PROGRAMMING MODEL

In the CR approach, the key element in the process of separating the computations from their dependencies is played by DDAs. Here, we abstract from the details of the separation methodology, and refer to Chapters 4, 5 and 6 for more details.

DDAs can also abstract over hardware communication layouts. Then the inherent flexibility of DDAs allows us to deal with embeddings at a high-level. A discussion of embeddings and ways to combine DDAs can be found in [Anderlik and Haveraaen, 2003; Haveraaen, 2009].

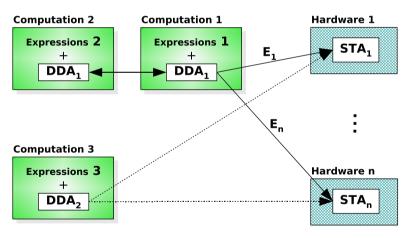

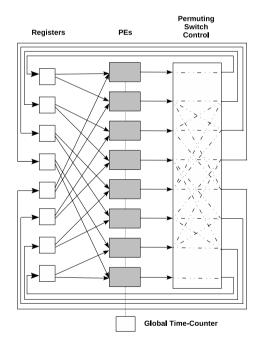

Figure 1.1: A Hardware Independent Parallel Programming Model

The conceptual overview of our programming model is presented in Fig. 1.1. The key elements of the model are:

- The data dependency pattern of a computation captured in the form of a *DDA* (e.g. DDA<sub>1</sub>). In practice, this means that the data dependency graph of the computation is expressed in the formalism of DDAs.

- The computation reformulated as *expressions* on the points of the DDA, such that dependencies between computational steps (DDA points) become explicit entities in the expression.

- A hardware architecture's space-time communication layout or API also captured by a special *space-time DDA* (STA) (e.g. STA<sub>1</sub>).

- The *embedding* of the computation by the means of a DDA-embedding (e.g. E<sub>1</sub>, E<sub>n</sub>). This is a task of finding a mapping of the computation's DDA onto the space-time DDA of the hardware.

- A *DDA-based compiler*, which for a given computation (e.g. computation 1) needs to be fed with:

- 1. the computation in terms of DDA<sub>1</sub> and the expressions over DDA<sub>1</sub>

- 2. the space-time DDA of the chosen hardware, e.g., STA<sub>1</sub>

- 3. the embedding  $E_1$  from DDA<sub>1</sub> to this space-time, STA<sub>1</sub>

Then the compiler generates code for the chosen hardware architecture. This can for instance be sequential code, CUDA code for GPUs, or vectorized C/C++ for the CELL/BE, and so on.

#### **Characteristics**

The model assumes that the space-time DDAs of the hardware architectures are predefined (e.g.  $STA_1,STA_2,\ldots$ ,  $STA_n$ ), and are associated with computational mechanisms in the DDA-enabled compiler. The programmer's task is to define the DDA of a computation, re-formalise the computation in term of this DDA, and define an embedding into the space-time DDA of the target architecture. For example,  $E_n$  from DDA<sub>1</sub> to the space-time DDA  $STA_n$ . The expressions on DDA<sub>1</sub> remain unchanged irrespective of the available hardware resource.

Since there is no need to rewrite the program solving code, the computation is *hardware independent* and *portable*. Also, there is no need for the compiler to do advanced parallelizing program analysis, as the embedding gives all the information needed for efficient parallel code generation. Alternative embeddings can easily be tested in search for optimal solutions,

since each embedding is defined explicitly, yet at a high, easy to manipulate, level.

The DDA-based programming model allows other kinds of *software re-usability* as well. Different computations may exhibit the same dependency pattern (DDA<sub>1</sub> in Computations 1 and 2), in which case all the embeddings defined for DDA<sub>1</sub> onto the different architectures can be reused. If a new computation exhibits a new dependency pattern (e.g. DDA<sub>2</sub> in Computation 3), all space-time DDAs, and associated execution models, are still available in the compiler, only new embeddings need to be defined into these, illustrated by dashed lines in Fig. 1.1.

DDAs, STAs and DDA-embeddings are discussed in Chapter 4. Language constructs for defining the computational expressions on DDA points are presented in Chapter 5. DDA-based execution models associated with space-time DDAs of different hardware architectures are also presented in Chapter 5. Examples instantiating these ideas are provided in Chapter 6. Mechanisms that promote automatic program refactoring in the compiler are presented in Chapter 7.

## 1.4 Contribution

The contributions of this dissertation are:

- it illustrates the role that DDAs can play in parallel computing by:

- giving a fresh perspective of the DDA concept

- demonstrating how the abstractions available in DDAs can control spatial placements of computations at a high-level

- showing how modern parallel hardware architectures' communication structure, such as GPUs, can be abstracted in terms of space-time DDAs

- further expanding the general theory of DDAs

- it presents the foundations of a DDA-based hardware independent parallel programming model

- it defines novel language constructs in accordance with the proposed programming model, and presents associated computational mechanisms for various hardware architectures (sequential, shared memory, GPUs and FPGAs)

- it formalises novel algebraic properties of DDAs that promote program refactoring

• it reports on preliminary practical results which underline that DDAbased embeddings of computations can be dealt with at high-level, and that DDA-based programming is portable

## 1.5 Published Results

This dissertation incorporates the following published works:

A Hardware Independent Parallel Programming Model, co-authored with Magne Haveraaen, and published in the *Journal of Logic and Algebraic Programming* by Elsevier Inc. [Burrows and Haveraaen, 2009b]. This is a joint work, with the basic ideas originating from Magne. It presents a significant contribution to the work previously published on DDAs, e.g., [Čyras and Haveraaen, 1995; Haveraaen, 2000, 1990a].

Dependency-Driven Parallel Programming, co-authored with Magne Haveraaen, and published in the Proceeding of Norsk Informatikk Konferanse (NIK) by Tapir [Burrows and Haveraaen, 2009a]. I am the main author with the work being supervised by Magne. The paper revisits the concept of DDAs in a gentle way, illustrates the results of the visualization tool, and comments on practical experiments.

#### 1.6 OUTLINE

This dissertation is organised as follows:

- Chapter 1 (this chapter) presents the conceptual overview of the proposed hardware independent parallel programming model.

- Chapter 2 reflects on the history of data dependency, focusing on how

dependence analysis influenced parallel computing research, and discusses some high-level parallel computing research directions of recent years.

- Chapter 3 gets the reader familiarized with mathematical terminologies used in the formal presentations, and introduces program code style conventions used in the program code examples.

- Chapter 4 revisits the formal definition of DDAs, giving a fresh perspective and understanding of what DDAs are, significantly expands the study of space-time DDAs and DDA-projections, presents new DDA concepts, related properties and relevant theorems, and defines new DDA examples.

#### 1. Introduction

- Chapter 5 proposes new language constructs, with precise syntax and semantics, designed to encapsulate a DDA-based computational expression, and presents various execution models, targeting different hardware architectures, which compute the semantics of the proposed constructs.

- Chapter 6 illustrates the essence of DDA-based programming by elaborating DDA-based solutions of well-known computational problems, and shows how these can be mapped to various hardware architectures at a high-level.

- **Chapter 7** gives a formal presentation of novel mechanisms that allow the building of compound DDAs from existing ones. The techniques presented promote program refactoring.

- **Chapter 8** discusses the achieved results, draws some conclusions, and points towards future directions.

CHAPTER 2

# Conquering Parallelism

Parallel computing research is about half a century old now. Throughout this period, most research directions aiming at tackling parallelism, in one way or another, always reflected the actual state-of-the-art of (parallel) computing systems. The steady developments of semi-conductor technology have influenced a great deal both the intensity and the enthusiasm at which researchers aimed at conquering parallelism.

Integrated circuit design had gone through a tremendous change. Moore [1965]'s prediction about the promising future of integrated circuits had been criticized, analysied and reformalized several times throughout the 70's, to adapt to the developments of semi-conductor industry. The 80's, however marked a breakthrough. The appearance of Very-large-scale Integration (VLSI) in circuit design allowed thousands of transistors to be combined into a single chip.

The appearance of first parallel systems, the vector processors of the 60-70's, brought forth much energy and launched a very optimistic and intense drive in automatic parallelization research. Much of this work looked back on the theoretical results of the 50's and 60's, which had already addressed some aspects of parallel and concurrent processing. The enthusiasm continued throughout the 80's, since despite the developments of VLSI uni-processor clock frequency did not increase as rapidly as expected. Supercomputers, on the other hand, were available, and many minisupercomputers began also to appear. This highly motivated parallel computing research, as increasing computing power throughput was primarily expected from exploiting the parallelism available on these machines.

The 90's ultimately justified Moore's law, as uni-processor speed began steadily to double every two years. This made uni-processors very appealing and more promising for achieving high computational throughput, for the masses at least. As a result, the driving force of parallel computing research has somewhat decreased, and became more of an interest for scientific computing communities.

By the end of 80's the focus from automatic parallelization research shifted towards programming language-based methods to explore parallelism. At the end of 90's, these efforts led to the standardization of OpenMP and MPI, which became the two dominant and very acceptable programming models for high-performance systems, even up to today.

The beginning of the millenium, however, marked a new era in parallel computing research. In 2005, Moore himself pointed out that his law cannot continue for ever, there are physical limits in the semi-conductor industry which ultimately cannot be pushed further to continuously increase uniprocessor speed. As a result, hardware vendors started to build multi-core architectures. The technology was ready, but programming methodologies were lacking. This reinvigorated parallel computing research and made it strive like never before, as parallelism had to be faced now on a daily basis.

In their excellent discourse [Asanovic et al., 2006] on the state-of-theart of parallel computing research, Berkeley researchers argue that current programming methodologies may be sufficient for systems with up to 8 processors, but they are not likely to scale beyond that. Inspired by the success of parallelism at the extremes of the computing spectrum, i.e., embedded computing and high-performance computing, the report suggests several design targets that a programming model should meet. The target is set to 1000 cores per chip, but programming models should not depend on the number of processors. Models should allow the user to indicate locality, and should support a wide range of data types. They should support well-known forms of parallelism: data-parallelism, task-parallelism, and instruction-level parallelism. Finally, instead of traditional benchmarks, they suggest new methods, borrowed from scientific computing, to design and evaluate programming models and architectures.

In the following two sections, we address only two slices of the vast topic of parallel computing research. The first, reflects on the history of data dependency, showing why dependence analysis became important, and how it influenced parallel computing research as a whole. The second presents some higher level parallel programming models that have emerged in the multi-core revolution era, and relates some of these approaches to our framework.

#### 2.1 A RETROSPECTIVE OF DATA DEPENDENCY

Early research on the theory of compiling high-level languages for high performance parallel systems was primarily based on program transformations. Dependence analysis provided execution-order constraints between program statements and as such served as a basis for establishing legitimate ways to carry out such transformations. The notion of *data dependency* describes one class of dependencies obtained throughout the process of dependence analysis.

Using data dependencies for program parallelization has a long and speckled history [Bacon et al., 1994; Wolfe and Banerjee, 1987]. Automatic parallelization, loop transformations, systolic arrays, dataflow programming, etc., are all connected to the notion of data dependency, which is fairly wide-spread in compiler design communities. The notion of *data dependency algebra* (DDA) – the key concept of this dissertation, is however less known.

In a general sense, dependencies are considered inherent in a program and low-level artifacts of the Von Neumann machine. As automatic dependence analysis proved to be too difficult for the general cases, the common understanding is that the limits of dependence analysis cannot be pushed much further to provide improved level of abstraction at which to think about parallelization.

The concept of DDA, on the other hand, points into a new direction. When the data dependency is made explicit in the program code (by means more expressive than just simple annotations), a parallelizing compiler can omit data dependence analysis as a whole, and yet harness directly the driving force of the dependency. Hence, DDAs increase the potential that data dependencies can play in program parallelization.

#### 2.1.1 Automatic Parallelization

At the dawn of computing when programs were written in the first high-level programming languages, the programmer naturally assumed that the results would be obtained by the machine executing the program statements in the order of their appearance, eventually, obeying any additional control flow constructs, such as if statements, goto-s, or similar branching mechanisms. Programs ran on primitive uni-processors, and there was no need for reordering the statements nor for identifying potential parallelism between the operations. When microprocessor technologies have become more advanced, with more sophisticated memory models, and the appearance of parallel computers, however, made compilers face fundamentally new challenges. For instance, when the micro-architecture was enabled to support

instruction pipelining, compilers had to explore instruction-level parallelism to make the most of the processors' instruction pipelining ability. Exploring data- and task-parallelism, however, placed a significantly heavier burden on both application developers as well as compiler designers.

For the programmer, the most appealing solution was the idea of *automatic parallelization*, when all the hassle of the parallelization process is cast on the compiler. The debate, however, was whether automatically generated parallel code could (ever) achieve the same performance as a handcoded parallel version.

The 1970's mark the beginnings of automatic parallelization research which set off as a joint effort to address portable programming on vector processors [Banerjee, 1976; Lamport, 1974; Loveman, 1976]. Hence this kind of parallelization is often referred to as *automatic vectorization*. A comprehensive overview of automatic program parallelization techniques is presented in [Banerjee et al., 1993]. In the search for program restructuring techniques, the technological tool developed was based on *dependence analysis* [Banerjee, 1988, 1996]:

"The aim of dependence analysis is to gather useful information about the underlying dependency structure of a program and present it in a suitable form. This analysis can be performed at various levels: we may study dependencies between program statements, iterations of a loop nest, subroutines in the program, etc." [Banerjee, 1996]

The compiler, based on a set of constraints, called *dependencies*, identifies when the reordering of program statements would not change the overall meaning of the program. These constraints are determined by the order in which program statements appear. The early work of Bernstein [1966] had a significant impact on the methods that were developed in the 70-80's.

Two major classes of dependencies have been identified: *control* and *data dependency*. These are usually represented as directed graphs in the compiler. An in-depth coverage of both methods can be found in [Wolfe, 1996] and [Kennedy and Allen, 2002]. When parallelizing or restructuring programs, as a general rule, both data and control dependencies need to be considered.

Control dependency relations provide a rather general method to capture the essential conditions controlling the execution of a program. Intuitively, control dependency occurs in a situation when a statement is executed if a previous statement evaluates in a way that allows its execution. For instance, in the following example:

```

S1: if a<>0

S2: b = b/a;

S3: c = 2:

```

the statement S2 is executed only if the execution of S1 evaluates to true. Hence S2 is control dependent on S1, whereas S3 is control independent.

Control dependency graphs are usually much larger than the associated control flow graphs. Two principal strategies were introduced to deal with control flow. The first, referred to as *if-conversion* in the literature, eliminates control dependencies by converting them into data dependencies. The second approach counts the control dependency as an extension of the data dependency by including edges of the control dependency graphs into the data dependency graph. These strategies were motivated by the fact that, during program analysis, it was easier to consider and argue about a single dependency graph.

The primary development regarding the use of control dependency in program transformation began with the work of Ferrante et al. [1987], and the framework for building efficient control dependency graphs originates from Cytron et al. [1991]. Various graph algorithms [Aho and Hopcroft, 1974] have been used to argue about the properties of control dependency graphs relevant in the context of program transformations and actual code generation processes, for example, finding strongly connected components of a directed graph. Significant contributions for the code generation process in the presence of control dependency can be found in [Kennedy and McKinley, 1990; McKinley, 1992].

Data dependency relations, on the other hand, ensure that data is provided and used in a correct order. These are less restrictive than control dependency relations, and give more flexibility in the transformation process. However, the order of memory references can be changed only to the extent that wrong values are not used or stored when the rearranged program is executed [Wolfe, 1996].

Three main classes of data dependency constraints are distinguished. Let S1 be a statement and S2 a subsequently executed statement. Then:

- S2 is *flow (or true) dependent* on S1, if S2 uses a variable which is assigned or previously modified in S1.

- S2 is *anti-dependent* on S1, if S2 reassigns a variable which has been used in S1.

- S2 is *output dependent* on S1, if a variable assigned in S1 is reassigned in S2.

The main data dependence problem for the compiler is to determine if two variables have instances that reference the same memory location during program execution [Banerjee, 1996]. The variables considered are usually either scalars or array elements in loop-iterations. In the latter case, the subscript expressions of the arrays are considered in the constraints [Allen, 1983]. The more complex the array subscripts are, the more complicated the dependence analysis becomes. Most accurate results could be obtained when the array subscripts were affine functions of the loop variables and they obeyed some additional properties [Maydan et al., 1995; Wolfe and Banerjee, 1987]. But in some cases, the constraints just simply could not be solved at all at compile-time, the compiler not having enough information.

The presence of procedure calls complicated significantly the process of dependence analysis [Burke and Cytron, 1986; Li and Yew, 1988]. Several early papers addressed the issues arising with interprocedural calls [Callahan et al., 1986; Cooper et al., 1986], but later new methods have been presented [Burke and Cytron, 2004; Müller-Olm, 2004] which solved many of these issues.

Due to these limitations, automatic vectorizers of simple sequential programs did not succeed in providing very significant high-performance. Nonetheless, the techniques based on dependence analysis became standards on most vector machines by the end of 1980's [Allen and Kennedy, 1987; Polychronopoulos et al., 1990; Wolfe, 1990].

With the appearance of shared and distributed memory architectures, automatic parallelization research turned towards exploiting these systems as well [Allen et al., 1988, 1987; Banerjee et al., 1993; Callahan and Kennedy, 1988; Kuck et al., 1980; Zima and Chapman, 1993]. Several additional aspects had to be considered, e.g., how to minimise the overhead of initiating and synchronizing parallel threads on shared memory systems, or how to partition data to the memories of the processors in distributed-memory systems with optimal communication [Amarasinghe and Lam, 1993], etc.

Dependence analysis became increasingly more complex, leading to long compiler running times, and the results did not demonstrate significant success as far as automatic parallelization was considered [Banerjee et al., 1993]. The techniques developed, however, had a great impact on the optimization techniques applied in most modern compilers [Kuck et al., 1980, 1981; Padua and Wolfe, 1986].

At the end of the 8o's, the automatic parallelization enterprise came to the conclusion that the long awaited high-performance was more likely to come from a joint effort [Dongarra et al., 2003, p. 361]. While still exploiting methods for automatic parallelization, the programmer should also

provide some useful information at the level of the program code. Hence, parallel programming language design began to explore language-based strategies that provided the compiler with additional information about data-decomposition, task- or data-parallelism. Some of these early research efforts led, for instance, to the standardization of High-Performance Fortran [Loveman, 1993] – a high-level data-parallel language based on Fortran –, which served as a basis for the upcoming generation of high-level parallel languages developed for high-performance systems, e.g., Fortran 95, OpenMP. The focus on language-based approaches, in the same time, naturally raised portability issues. Explicit representation of parallelism in the source code did not guarantee optimal use of parallel hardware. If one way of expressing parallelism worked well on one architecture, this most likely needed to be altered when ported to another system due to performance-related considerations.

## 2.1.2 Restructuring Compilers

As loops tended to be the most time-consuming parts of the programs, program restructuring methods were first highly focused on these. *Loop-based transformations* promised to deliver increased parallelism as well as optimized running time. The first high-level parallel language constructs were also designed to express loop-level parallelism, for the same reason.

Loop-transformations were based on elaborate *dependence tests* of entire loop nests and across subscripts of possibly multiple arrays. Based on these methods, several strategies have been developed for various loop-level transformations, e.g., loop interchange, loop skewing, loop fusion, loop reordering, loop unfolding, loop tiling etc.

In the general cases, these tests became very complex. Low-complexity tests, luckily, produced quite accurate results in many cases, such as the GCD test [Psarris, 1996], the I-Test [Kong et al., 1991], and Banerjee's Inequilities [Banerjee, 1979; Psarris, 1992]. The Omega test [Feautrier, 1988; Pugh and Wonnacott, 1992], a constraint-based analysis, was an independent effort to improve array dependence analysis which provided exact results for affine cases. While it was exponential for the general cases, it often provided faster results than its fellow competitors for the common cases. The Omega test is often related to the polyhedral model [Pouchet et al., 2008]. This is a mathematical framework based on affine transformations of dependencies, useful in program restructuring, such as tiling [Gupta et al., 2007].

While the idea of purely automatic parallelization did not succeed the way it was hoped for, the vast amount of knowledge gathered about de-

pendence analysis contributed a great deal to building powerful optimizing compilers. [Bacon et al., 1994] is a concise and comprehensive survey of the state-of-the-art of dependence-based transformations of the pre-Fortran 95 era. Wolfe [1996] provides a more technical presentation, and Kennedy and Allen [2002] discusses further developments. Dependence-based approaches have remained crucial in advanced program analysis and transformation techniques in modern compiler design [Srikant and Shankar, 2007].

Research directions for developing more accurate and faster algorithms for dependence tests are still noticeable. A recent comparison of data dependence analysis tests can be found in [Viitanen and Hämäläinen, 2004]. A new dependence analysis tool is described by Kyriakopoulos and Psarris [2005], which empirically is proved to be more efficient in program parallelization than usual dependence tests. Zhou and Zeng [2006] present a more general scheme of dependence test based on integer interval theory to solve difficult dependence test problems.

# 2.1.3 Data-driven Paradigms

Also inspired by the inherent data and flow dependency of computations, the 1970's brought forth other approaches which meant to exploit parallelism in a different way. As hardware were becoming (relatively) less expensive, special purpose micro-architectures began to appear especially designed for signal and image processing. Based on these experiments, new data-driven architecture models evolved as a contrast to the von Neumann instruction-driven paradigm.

The term *systolic array* was coined by Kung and Leiserson [1978]. A systolic system was presented as a regular pipe network arrangement of processors, called *cells*, which computed and passed data through the system rhythmically. Hence the name analogy with the regular pumping of blood by the heart. Since the data was organised as multiple data streams, the underlying idea well-supported data parallelism, and the regularity of the network ensured scalability.

Systolic array research primarily focused on designing algorithms and architectures that laid out well in two dimensions so that they could adapt well to VLSI technology restrictions [Kung, 1982]. The shape of the cell-network varied, e.g., rectangular, triangular or hexagonal, each exploiting higher degree of parallelism in a different way. The actual interconnects between the cells modeled the dataflow of the algorithm that the systolic array was built for. Hence exploiting the flow and data dependency of an algorithm was a key element in the design of systolic arrays, e.g.,

[Jen and Kwai, 1992; McCanny et al., 1990]. Miranker and Winkler [1984] presented a general theory for characterizing and realising algorithms in hardware. The approach was based on data dependency graphs of computations embedded into space-time representations of hardware. The technique developed described the mapping of a particular systolic algorithm into a physical array.

Many systolic algorithms have been proposed, e.g., for matrix arithmetic, data- and graph-algorithms, signal and image processing. They had the potential of taking an exponential algorithm and turn it into a linear-time hardware implementation. However, the building of a systolic array parallelizing compiler that could translate a high-level scientific code for systolic arrays remained challenging.

Despite their great potential for massive parallelism, high throughput, and gradual support for SIMD organizations for vector operations and MIMD for non-homogeneous parallelism, systolic arrays were expensive and hard to build. Due to their inherent characteristics, systolic architecture design, nonetheless, has prevailed, e.g., in reconfigurable computing.

The *dataflow machine* was another data-driven programmable computer which had a specialised hardware optimised for fine-grain data-driven parallel computations. The concept originates back to the 60's when dataflow graphs were first developed [Davis, 1979]. The first implementation of a dataflow machine points back to 1976 [Davis, 1979]. Dataflow architectures disregard from the general notion of program counter, and promote explicit data-driven execution. A survey of early machines can be found in [Veen, 1986]. Dataflow languages have also emerged (e.g., Sisal, Lustre, Lucid, VHDL, etc.).

Binaries compiled for a dataflow machine contain dependency information, which is usually not common to binaries. This information is utilised when the program is executed on the machine, and by a special mechanism it can decide over code segments that can be executed in parallel.

Dataflow machines have been primarily implemented as specialized hardware used in digital signal processing, network routing and graphics processing.

# 2.1.4 Parallel Functional Languages in the 90's

Under the flagship of automatic parallelization research, functional languages also emerged as potential candidates. The basic computational abstractions of a functional language are functions. Since a functional program has no such notion as execution state and has a value-oriented semantics, it usually requires a simpler dependence analysis, at the cost of more complex

data allocation and modification operations. The key question in parallel functional languages was how much parallelism can be extracted automatically and how much should be provided by the programmer. Data partitioning was one of the issues that required additional information. A nice compilation of parallel functional compiler directions of this period can be found in [Szymanski, 1991], including PTRAN, the HPF compiler. Some of these were heavily based on dependence graph transformations in the code generation process.

In particular, EPL and Crystal followed a transformation strategy based on equational annotations, aiming at generating optimized and efficient implementations for a variety of hardware. The optimization of Crystal programs followed a series of systematic transformations of data index-spaces, automated by the compiler, until an optimal data distribution was found which matched the physical characteristics of the given hardware. Both languages hinted that modelling the hardware architectures' physical properties at a higher abstraction level in the compiler would be beneficial in the code generation process.

The book [Szymanski, 1991] also exposes the philosophy of dataflow programming by presenting Sisal, Lucid and Id.

# 2.1.5 Explicit Data Dependency

As mentioned earlier, Miranker and Winkler [1984] introduced a general theory about embedding the data dependency graph of a computation into the space-time topology of a systolic array. Haveraaen [1990b, 2000, 1990a] took this underlying idea further when developing the *constructive recursive* (CR) approach. This allowed the modular separation of computation from its dependencies, such that both became programmable independently from each other. This also entailed a separation between local dependencies of a function, and the global communication pattern of the whole computation in the hardware. The idea showed many similarities with the *structural blanks approach* of Čyras, and both techniques were presented and compared in [Čyras and Haveraaen, 1995].

Haveraaen's approach was based on algebraic abstractions, referred to as *Data Dependency Algebras* (DDA). DDAs provided a formalism to express data dependencies as explicit, first class, programmable entities in the program code. This makes Haveraaen's approach rather unique, compared to previous frameworks. The extracted data dependencies are primarily true (flow) data dependencies.

As Banerjee [1996] put it, the aim of dependence analysis was to gather useful information about the underlying data dependency structure of a

program and present it in a suitable form. A DDA delivers exactly this information to the compiler, and it comes from the effort of the programmer, and not of the compiler. The programmer analyses the underlying dependency by the means of pencil, scratch paper and human intelligence. If the attempt is successful, the result is a concise, meaningful representation of the data dependency pattern of the computation in the program code, ready to be used by a parallelizing compiler.

The prototype compiler implemented by Søreide [1998] followed an optimised recursion unfolding strategy in the code generation process. This was entirely based on the information provided in the DDA. The compiler adapted a technique inspired by tail recursion optimization, as common to many functional languages, developing it to arbitrary, not just linear, dependency patterns.

Later, Burrows and Haveraaen [2009b] presented a unified programming model based on the basic idea of CR, showing that DDAs provide a high-level, flexible and hardware independent formalism to deal with parallelism. This served as starting point for this dissertation.

## 2.2 HIGH-LEVEL APPROACHES IN THE MULTI-CORE ERA

Research directions of earlier times are often revisited. In hindsight it is often easier to understand why a very promising approach did not succeed. High-Performance Fortran (HPF) is one of these [Kennedy et al., 2007]. HPF was accepted with great enthusiasm in the early 90's. However, the initial excitement has faded out. This is attributed to reasons that are worth learning from: immature compiler technology leading to poor performance, lack of flexible distributions, inconsistent implementations, missing tools, and lack of patience by the high-performance computing community. Although HPF itself failed to achieve success, it had a great impact on the development of high-level parallel languages (e.g. Fortran 95, OpenMP, Chapel, Fortress, X10).

In recent years, several new programming models have been proposed, and in some cases implemented. However, the underlying basic ideas point back to approaches from decades ago. In general, they come in either a task parallel or data-parallel fashion, though the latter seems to outweigh the former as to popularity. This should not come as a surprise, since data-parallelism, by its nature, scales better with growing number of processors.

Some of the current programming models targeting multi-core and/or GPU programming in imperative style are:

- CellSs [Perez et al., 2007] has been proposed as an alternative task

parallel programming model for multi-core processors, and its current implementation targets IBM's CELL/BE processor. It is based on

the automatic exploitation of the functional parallelism of a sequential program through the different processing elements of the Cell/BE

architecture. It is based on annotations to a sequential code, similar to

that of OpenMP.

- Also on the task parallel front, with Intel's TBB library [Reinders, 2007] one can express parallelism in a C++ program. It is based on a higher-level, task-based parallelism that abstracts platform details and threading mechanism for performance and scalability.

- Intel's Array Building Blocks [Intel, 2010] provides a generalized vector parallel programming solution that abstracts from the dependencies on particular low-level parallelism mechanisms or hardware architectures. It produces scalable, portable, and deterministic parallel implementations from a single high-level source description.

- RapidMind [Monteyne, 2008] is a development and runtime platform

to a variety of architectures, including GPUs, the Cell/BE, and multicore CPUs. It is a data-parallel programming model which takes a

high-level abstraction of parallelism and maps it to what is available.

A recent article discusses its limitations [Christadler and Weinberg,

2011]. RapidMind is now part of Intel, and the technology is integrated into Intel's Array Building Blocks.

- Microsoft Research's Dryad [Isard et al., 2007] is a general-purpose distributed execution engine for coarse-grain data-parallel applications. It combines computational vertices with communication channels to form a dataflow graph. The user can specify a directed graph to describe the application's communication patterns between the computation vertices.

- A heterogeneous data-parallel computational model for the Cell/BE has been recently presented in [Li et al., 2008]. It proposes to aggregate the computing power of the two different processing elements of the Cell/BE, i.e., of the synergistic processor elements, and of the heavy duty processor element.

- Huckleberry [Collins et al., 2010] is an experimental tool which automatically generates parallel implementations for multi-core platforms from sequential recursive divide-and-conquer programs.

- The Sequoia [Fatahalian et al., 2006] programming language facilitates

the development of memory hierarchy aware parallel programs that

remain portable across modern architectures and controls data locality. It provides language mechanisms to describe communication vertically through the machine and to localize computation to particular

memory locations within it.

- The partitioned global address space (PGAS) [PGAS, 2010] is a relatively new parallel programming model which serves as a basis for several new high-level parallel languages, such as Unified Parallel C, Co-array Fortran, Fortress, Chapel and X10. The model assumes that the global memory space is logically partitioned. Each portion becomes local to each processor, and it may also have an affinity for the particular thread running on the processor, thereby exploiting data locality.

- ParaMeter [Kulkarni et al., 2009] is a tool which can determine how much parallelism is latent in irregular programs wich exhibit amorphous data-parallelism. It produces parallelism profiles for the programs in question, and the methodology used is based on graphrepresentations.

Declarative approaches also tackle multi-core and GPU programming. Since declarative languages offer a pure view of computation, such settings are suitable to express data-parallelism in high-level descriptions [Lisper, 1996].

- Singh [2008] argues about the importance of the ability to target different computing devices from the same description. He shows how GPUs and FPGAs can be targeted from a single data-parallel description, based on higher order functions and polymorphism.

- Data Parallel Haskell [Chakravarty et al., 2007] aims to implement the programming model of nested data-parallelism into the Glasgow Haskell Compiler, by extending NESL [Blelloch et al., 1994] in terms of expressiveness and efficiency. NESL is a portable nested data-parallel language, appeared in the early 90's, which allows high-level, concise descriptions of nested data-parallel programs.

- Obsidian [Svensson, 2011] is a data-parallel language embedded in Haskell which targets GPU programming. The current version is implemented for NVIDIA's CUDA. The programming style is inspired by Lava combinators [Bjesse et al., 1999], high-level structural hardware design elements.

- Skeletal parallel programming evolved from the idea of higher-order function applications [Cole, 1989]. *Skeletons* ("higher-order functions") are high-level parallel constructs, which describe computational structures without over-specifying the details. They come as library packages with efficient implementations for the different parallel systems. The programmer identifies the patterns that fit his need, and customizes them by filling in the "arguments". These can be other functions/procedures to which the skeleton is applied to produce the problem specific final program [Cole, 2004; Rabhi and Gorlatch, 2003].

- Feldspar [Axelsson et al., 2010] is a domain-specific language, embedded into Haskell, which enables high-level and platform-independent description of digital signal processing algorithms. It offers a high-level dataflow style of programming.

Few, if any, of these programming models represent fundamentally new ideas. Task parallelism goes back to the 60's idea of concurrent processes [Hansen, 1973] with shared memory. Message passing style parallelism goes back to the mid 70's [Hoare, 1978] and its foundation has been investigated in several process algebras from the 80's onwards. Data-parallelism evolved from systolic arrays, and was a firmly established approach by the mid-80's [Hillis and Guy L. Steele, 1986] when it was the main programming model for some of that time's high-end parallel machines. A wide variation of early parallel programming models are surveyed in [Baer, 1973], and a good literature list can be found in [Hibbard, 1980].

Our approach is data-parallel by considering the entire computation at once. We emphasize modular separation of the computational expressions from the data dependency, and separation of the dependency from its embedding onto hardware. The latter allows us to fully control resource usage, including data locality. This separates us from most functional approaches, though our expression-oriented notation would be considered functional.

The focus on dataflow graphs is in common with the ParaMeter and the Dryad approach. In the latter, the graphs, in response to some events that occur during the computation, can change dynamically. Our dependency graphs are fixed throughout the whole computation, and the DDA-based approach targets fine-grain data-parallelism.

The dataflow execution model, originally developed to exploit massive parallelism [Johnston et al., 2004], had a great effect in the development of dataflow visual programming languages. In this model a program is represented as a directed graph. The nodes of the graph are primitive instructions such as arithmetic or comparison operations, and the arcs between

the nodes represent the data dependencies between the instructions. This makes the dataflow programming model related to ours, however, it differs in one fundamental aspect. In the dataflow programming model, the main concept behind any program is the *data*. In the DDA-based approach, it is the *dependency* which is promoted as first class citizen.

Automatic parallelization techniques of regular, loop-based applications, based on compile time dependence analysis [Banerjee et al., 1993], are also related to our approach. It has also been known for some time that compilers can parallelize divide-and-conquer programs by analyzing memory references to detect dependencies [Gupta et al., 2000; Rugina and Rinard, 1999]. The above mentioned Huckleberry tool is also based on this technique, and is related to our approach to the extent that it also utilises data dependency information in the parallelization process. However, in DDA-based parallelization, the compiler is fed with the data dependency, and need not bother about advanced parallelizing program analysis. The information given in the DDA is sufficient for efficient parallel code generation, and offers more flexibility when it comes to mapping the computation onto different parallel hardware architectures. In addition, the DDA-based approach is more general, and not tied to only divide-and-conquer algorithms and loop-based applications.

# CHAPTER 3

# **Preliminaries**

Before embarking on the formal presentation of our subject, we recall the mathematical notions relevant in the context of this dissertation, fix the notations, and introduce program code style conventions together with some data type abstractions assumed to be present in the examples. The reader is assumed to be acquainted with elementary set and graph theory as well as general programming language concepts.

#### 3.1 MATHEMATICS

## 3.1.1 Sets

By set we mean a collection of elements. Some particular sets are:

- the set of natural numbers, denoted by the symbol  $N = \{0,1,2,\ldots\}$

- non-zero elements of N, denoted by  $N^+ = \{1,2,\ldots\}$

- set of real numbers, denoted by R

- set of complex numbers, denoted by  $C = \{a + bi \mid a, b \in R\}$ , where i is the *imaginary unit* with the property  $i^2 = -1$

- the two-element set of truth values, denoted by  $\mathbf{B} = \{0, 1\}$

- the empty set with no elements at all, denoted by {}

The *cardinality of a set A*, often denoted by |A|, is the *number of elements* in A. A *finite set* has a finite number of elements. A set that is not finite is called *infinite*. A set is *countable* if it has at most the same cardinality as the set of natural numbers. A set that is not countable is *uncountable*. E.g. the set of real numbers is uncountable.

The following notations, operations and related properties are common to sets:

- $A \subseteq B A$  is a *subset* of B, if all elements of A are also in B

- $A \subset B A$  is a proper subset of B, if  $A \subseteq B$  but  $A \neq B$

- $A \setminus B = \{a \mid a \in A \text{ and } a \notin B\}$  the difference of A and B

- $A \cup B = \{a \mid a \in A \text{ or } a \in B\}$  the *union* of A and B

- $A \cap B = \{a \mid a \in A \text{ and } a \in B\}$  the *intersection* of A and B. If  $A \cap B = \{\}$  then A and B are called *disjoint*

- $A_{i,c} = \{\langle a,i \rangle \mid a \in A_i\}$  the *canonical form* of set  $A_i$  wrt. some indexset I, where  $i \in I$ .

- $A_1 \uplus A_2 = A_{1,c} \cup A_{2,c}$  the *disjoint union* of  $A_1$  and  $A_2$ . The elements of the disjoint union are ordered pairs  $\langle a,i \rangle$ , where the index  $i \in \{1,2\}$  indicates exactly which set  $A_i$  the element a comes from in the pair  $\langle a,i \rangle$ .

- $A_1 \times A_2 \times \ldots A_k = \{\langle a_1, a_2, \ldots, a_k \rangle \mid a_i \in A_i, \ 1 \le i \le k\}$  the *cartesian product* of the sets  $A_1, A_2, \ldots, A_k$  with  $k \ge 0$ . If k = 0 or one of the sets is the empty set, then the cartesian product is also the empty set.

Note that one may use the cartesian product to construct the canonical form of a set  $A_{i}$ ,  $i \in I$ :

$$A_{i,c} = A_i \times \{i\} = \{\langle a, i \rangle | a \in A_i\}$$

**Theorem 3.1.1.** The union, intersection and disjoint union of sets obey the following laws:

• Commutativity:

$$A_1 \cup A_2 = A_2 \cup A_1 \tag{3.1}$$

$$A_1 \cap A_2 = A_2 \cap A_1 \tag{3.2}$$

$$A_1 \uplus A_2 = A_2 \uplus A_1 \tag{3.3}$$

• Associativity:

$$(A_1 \cup A_2) \cup A_3 = A_1 \cup (A_2 \cup A_3) \tag{3.4}$$

$$(A_1 \cap A_2) \cap A_3 = A_1 \cap (A_2 \cap A_3) \tag{3.5}$$

$$(A_1 \uplus A_2) \uplus A_3 = A_1 \uplus (A_2 \uplus A_3) \tag{3.6}$$

*Proof:* Properties 3.1, 3.2, 3.4 and 3.5 are straightforward from the definitions. The commutativity (3.3) and associativity (3.6) of disjoint union follow from the observation that the disjoint union is obtained through the embeddings of the participating sets' canonical forms, i.e.:

$$A_1 \uplus A_2 = A_{1,c} \cup A_{2,c} = A_{2,c} \cup A_{1,c} = A_2 \uplus A_1$$

and

$$A_1 \uplus (A_2 \uplus A_3) = A_{1,c} \cup (A_{2,c} \cup A_{3,c}) = (A_{1,c} \cup A_{2,c}) \cup A_{3,c} = (A_1 \uplus A_2) \uplus A_3$$

These properties lead to the following generalized forms extended over a family of sets  $(A_i)_{i \in I}$  for some index-set I:

- Union:  $\bigcup_{i \in I} A_i = \{ a \mid a \in A_i \text{ for some } i \in I \} \text{ and } \bigcup_{i \in \{\}} A_i = \{ \} \}$

- Disjoint union:  $\biguplus_{i \in I} A_i = \bigcup_{i \in I} \{\langle a, i \rangle | a \in A_i\}$  and  $\biguplus_{i \in \{\}} A_i = \{\}$

- Intersection:  $\bigcap_{i \in I} A_i = \{a \mid a \in A_i \text{ for all } i \in I\}$

#### 3.1.2 Arithmetics

Given  $n \in \mathbb{N}^+$ , then the *n-th root of unity* is a complex number  $z \in \mathbb{C}$  satisfying the equation:

$$z^n = 1$$

The *n*-th root of unity is *primitive*, if it is not a *k*-th root of unity for some  $k \in \mathbb{N}^+$  such that k < n, that is:

$$z^k \neq 1$$

The *Euler formula* establishes a relationship between the trigonometric functions and the complex exponential function stating that for any  $x \in \mathbb{R}$ :

$$e^{ix} = \cos x + i \sin x$$

where e is the base of the natural logarithm and i is the imaginary unit. The Euler formula is used then to transform the formula for the n-th roots of unity into its most familiar form:

$$e^{2\pi i \frac{k}{n}}$$

This will be a primitive root if and only if the fraction k/n is in lowest terms, that is their greatest common divisor is 1.

#### 3.1.3 Relations

If *A* and *B* are sets, then a *relation* between *A* and *B* is defined as a subset of their cartesian product, i.e.,  $R \subseteq A \times B$ . When A = B, one says that *R* is a relation *on A*.

We will often use the shorthand R(a,b) for  $\langle a,b\rangle \in R$ .

A relation *R* on *A* is called:

- *trichotomous*, if for all  $a,b \in A$  exactly one of the following holds: R(a,b), R(b,a) or a=b;

- *reflexive*, if for all  $a \in A$ : R(a, a);

- *symmetric*, if for all  $a, b \in A$ : R(a, b) implies R(b, a);

- *transitive*, if for all  $a, b, c \in A$ : R(a, b) and R(b, c) implies R(a, c);

- equivalence relation, when it is reflexive, symmetric and transitive;

- strict total order, when it is trichotomous and transitive.

For instance, the relation "<" on the set of natural numbers is a strict total order, and so is the standard dictionary order with the letters of the latin alphabet, whereas "=" on the set of natural numbers is an equivalence relation.

#### 3.1.4 Functions

If *A* and *B* are non-empty sets, and *f* is a relation between *A* and *B*, then *f* is called:

- a *partial function* from A to B, denoted by  $f: A \leadsto B$ , if for every element  $a \in A$  there exists no or at most one  $b \in B$  such that  $\langle a, b \rangle \in f$ .

- a *total function* from *A* to *B*, denoted by  $f: A \to B$ , if for every element  $a \in A$  there exists exactly one  $b \in B$  such that  $\langle a, b \rangle \in f$ .

One then writes f(a) = b, where a is called *argument* and b the *value* of f in a. If f is a partial function, and there exists no  $b \in B$  such that f(a) = b then one says that f(a) is *undefined*.

*A* is called the *domain* of *f* , and *B* its *codomain*.

All functions are assumed to be total, unless explicitly stated otherwise. If A and B are the empty sets, then  $f:\{\} \rightarrow \{\}$  is called the *empty function*.

A predicate is a function with the set  $\bf B$  as its codomain.

If f is a function with some cartesian product as its domain, e.g.  $A \times B$ , we may omit the use of bracketing for the elements when they appear as arguments, e.g., we write f(a,b) instead of  $f(\langle a,b\rangle)$  for  $\langle a,b\rangle \in A \times B$ .

Given functions  $f: A \to B$  and  $g: B \to C$ , the *composition* of g to f is the function  $g \circ f: A \to C$  defined by:

$$(g \circ f)(a) = g(f(a))$$

for all  $a \in A$

**Theorem 3.1.2.** The composition of functions is associative, i.e., if  $f: A \rightarrow B$ ,  $g: B \rightarrow C$  and  $h: C \rightarrow D$  are functions then:

$$(h \circ g) \circ f = h \circ (g \circ f)$$

*Proof:* For all  $a \in A$  we have:

$$((h \circ g) \circ f)(a) = (h \circ g)(f(a)) = h(g(f(a))) = h((g \circ f)(a)) = (h \circ (g \circ f))(a)$$

The *identity function* of a set A is the function  $\mathbf{1}_A:A\to A$  defined by  $\mathbf{1}_A(a)=a$  for all  $a\in A$ .

A function  $f: A \to B$  is called an *isomorphism*, if there exists a function  $f^{-1}: B \to A$ , called its *inverse*, such that  $f \circ f^{-1} = 1_B$  and  $f^{-1} \circ f = 1_A$ . One may also call then the sets A and B isomorphic, and write  $A \simeq B$ .

**Theorem 3.1.3.** The inverse of an isomorphism is unique.  $\Box$

*Proof:* Let  $f: A \to B$  be an isomorphism with inverse  $f^{-1}: B \to A$ , i.e.,  $f \circ f^{-1} = 1_B$  and  $f^{-1} \circ f = 1_A$ . Assume there exists also inverse  $f': B \to A$  such that  $f \circ f' = 1_B$  and  $f' \circ f = 1_A$  also. Then we have for all  $b \in B$ :

$$f'(b) = \mathbf{1}_{A}(f'(b)) \qquad \text{(by def. of } \mathbf{1}_{A})$$

$$= (\mathbf{1}_{A} \circ f')(b) \qquad \text{(by def. of } \circ)$$

$$= ((f^{-1} \circ f) \circ f')(b) \qquad \text{(assumption)}$$

$$= (f^{-1} \circ (f \circ f'))(b) \qquad \text{(by Th. 3.1.2)}$$

$$= (f^{-1} \circ \mathbf{1}_{B})(b) \qquad \text{(assumption)}$$

$$= f^{-1}(\mathbf{1}_{B}(b)) \qquad \text{(by def. of } \circ)$$

$$= f^{-1}(b) \qquad \text{(by def. of } \mathbf{1}_{B})$$

Hence  $f' = f^{-1}$ .

A function  $f: A \to B$  is called *injective* if for all  $a, b \in A$  with f(a) = f(b) implies that a = b. f is called *surjective* if for all  $b \in B$  there exists  $a \in A$  such that f(a) = b. An injective and surjective function is called *bijective* or a *bijection*.

**Theorem 3.1.4.** A function  $f: A \to B$  is bijective if and only if it has an inverse.

*Proof:* ( $\Rightarrow$ ) Assume f is bijective. Then we define  $g: B \to A$  the inverse of f as follows: for each  $b \in B$  there exists  $a \in A$  such that b = f(a) (since f is surjective). a is also unique since f is injective. Then let g(b) = a. Then  $(g \circ f)(a) = g(f(a)) = g(b) = a$  for each  $a \in A$ . And  $(f \circ g)(b) = f(g(b)) = f(a) = b$  for each  $b \in B$ .

(⇐) Assume now that  $g: B \to A$  is the inverse of f. Then f is injective since f(a) = f(b) implies g(f(a)) = g(f(b)), that is  $(g \circ f)(a) = (g \circ f)(b)$ , that is, a = b. And f is also surjective: Let  $b \in B$  arbitrary, and set a = g(b). Then  $f(a) = f(g(b)) = (f \circ g)(b) = b$ .

If  $f: A \to B$  is a function and  $C \subseteq A$ , then the *restriction* of f to C is the function  $f|_C: C \to B$  defined by:

$$f|_{C}(a) = f(a)$$

for all  $a \in C$

A binary operator over a set A is given by a function  $f: A \times A \rightarrow A$ .

## 3.1.5 Graphs